# Simulink® HDL Coder™ Release Notes

#### How to Contact The MathWorks

www.mathworks.com

comp.soft-sys.matlab

www.mathworks.com/contact TS.html Technical Support

Web

Newsgroup

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com

service@mathworks.com info@mathworks.com

Product enhancement suggestions

Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Simulink® HDL Coder<sup>TM</sup> Release Notes

© COPYRIGHT 2007-2010 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

## Contents

| Summary by Version                                        | 1  |

|-----------------------------------------------------------|----|

| Version 1.7 (R2010a) Simulink® HDL Coder Software         | 4  |

| Version 1.6 (R2009b) Simulink® HDL Coder Software         | 13 |

| Version 1.5 (R2009a) Simulink® HDL Coder Software         | 25 |

| Version 1.4 (R2008b) Simulink® HDL Coder Software         | 36 |

| Version 1.3 (R2008a) Simulink® HDL Coder Software         | 48 |

| Version 1.2 (R2007b) Simulink® HDL Coder Software         | 64 |

| Version 1.1 (R2007a) Simulink® HDL Coder Software         | 73 |

| Compatibility Summary for Simulink® HDL Coder<br>Software | 76 |

### **Summary by Version**

This table provides quick access to what's new in each version. For clarification, see "Using Release Notes" on page 1.

| Version<br>(Release)            | New Features<br>and Changes | Version<br>Compatibility<br>Considerations | Fixed Bugs<br>and Known<br>Problems | Related<br>Documentation<br>at Web Site            |

|---------------------------------|-----------------------------|--------------------------------------------|-------------------------------------|----------------------------------------------------|

| Latest Version<br>V1.7 (R2010a) | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                         | Printable Release<br>Notes: PDF<br>Current product |

| V1.6 (R2009b)                   | Yes<br>Details              | Yes<br>Summary                             | None                                | No documentation                                   |

| V1.5 (R2009a)                   | Yes<br>Details              | Yes<br>Summary                             | None                                | No                                                 |

| V1.4 (R2008b)                   | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                         | No                                                 |

| V1.3 (R2008a)                   | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                         | No                                                 |

| V1.2 (R2007b)                   | Yes<br>Details              | Yes<br>Summary                             | Bug Reports                         | No                                                 |

| V1.1 (R2007a)                   | Yes<br>Details              | No                                         | Bug Reports                         | No                                                 |

#### **Using Release Notes**

Use release notes when upgrading to a newer version to learn about:

• New features

- Changes

- Potential impact on your existing files and practices

Review the release notes for other MathWorks<sup>™</sup> products required for this product (for example, MATLAB® or Simulink®). Determine if enhancements, bugs, or compatibility considerations in other products impact you.

If you are upgrading from a software version other than the most recent one, review the current release notes and all interim versions. For example, when you upgrade from V1.0 to V1.2, review the release notes for V1.1 and V1.2.

#### What Is in the Release Notes

#### **New Features and Changes**

- New functionality

- Changes to existing functionality

#### **Version Compatibility Considerations**

When a new feature or change introduces a reported incompatibility between versions, the **Compatibility Considerations** subsection explains the impact.

Compatibility issues reported after the product release appear under Bug Reports at The MathWorks<sup>TM</sup> Web site. Bug fixes can sometimes result in incompatibilities, so review the fixed bugs in Bug Reports for any compatibility impact.

#### **Fixed Bugs and Known Problems**

The MathWorks offers a user-searchable Bug Reports database so you can view Bug Reports. The development team updates this database at release time and as more information becomes available. Bug Reports include provisions for any known workarounds or file replacements. Information is available for bugs existing in or fixed in Release 14SP2 or later. Information is not available for all bugs in earlier releases.

Access Bug Reports using your MathWorks Account.

#### **About Functions and Properties Being Removed**

This section lists functions or properties removed or in the process of being removed. Functions and properties typically go through several stages across multiple releases before being completely removed. This provides time for you to make adjustments to your code.

- Announcement The Release Notes announce the planned removal, but there are no functional changes; the function runs as it did before.

- Warning When you run the function, it displays a warning message indicating it will be removed in a future release; otherwise the function runs as it did before.

- Error When you run the function, it produces an error. The error message indicates the function was removed and suggests a replacement function, if one is available.

- Removal When you run the function, it fails. The error message is the standard message when MATLAB does not recognize an entry.

Functions and properties might be in a stage for one or more releases before moving to another stage. Functions and properties are listed in the Functions and Properties Being Removed section only when they enter a new stage and their behavior changes. For example, if a function displayed a warning in the previous release and errors in this release, it appears on the list. If it continues to display a warning, it does not appear on the list because there was no change between the releases.

Not all functions and properties go through all stages. For example, a function's impending removal might not be announced, but instead, the first notification might be that the function displays a warning.

The Release Notes include actions you can take to mitigate the effects of function or property removal, such as adapting your code to use a replacement function.

### Version 1.7 (R2010a) Simulink HDL Coder Software

This table summarizes what's new in Version 1.7 (R2010a):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations                                                | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site                    |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------|

| Yes<br>Details below        | Yes—Details labeled<br>as Compatibility<br>Considerations,<br>below. See also<br>Summary. | Bug Reports                      | Printable Release Notes: PDF Current product documentation |

New features and changes introduced in this version are:

- "Simplified Syntax for Specification of Block Implementations in Control Files" on page 5

- "HDL Workflow Advisor" on page 7

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 8

- "CORDIC Algorithm Supported for Trigonometric Functions (sin, cos, sincos)" on page 9

- "Option to Minimize Generation of Clock Enables" on page 10

- "VHDLArchitectureName Property Supports Specification of Architecture Name" on page 10

- "VHDLLibraryName Property Supports Specification of Target Library" on page 10

- "Output Pipelining Now Supported for Subsystems" on page 10

- "Distributed Pipelining Now Supported for Subsystems" on page 11

- "CSD and Factored CSD Optimizations for Constant Multiplications" on page 11

- "Enhanced Gain Block Support" on page 11

- "FIR Decimation Filter Supports Distributed Arithmetic Architecture" on page 12

- "Serial, Partly Serial and Cascade Serial Architectures Supported for FIR Filter Implementations" on page 12

- "InstancePostfix Property Allows Specification of Extension to Postfix String" on page 12

### Simplified Syntax for Specification of Block Implementations in Control Files

In R2010a, the coder supports a simplified syntax for specifying block implementations in a control file. The new syntax lets you specify a block implementation using simple keywords, instead of package.class notation. The new implementation keywords are generic, rather than block-specific. This approach lets you use the same keyword to specify implementation types such as Tree, Cascade, or Linear for all blocks that support such implementations. For example, the following control file specifies that the coder uses a cascade implementation for all Sum blocks and all Product blocks in the model.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

cfg.forEach('*',...

'built-in/Sum', {},...

'Cascade', {});

cfg.forEach('*',...

'built-in/Product', {},...

'Cascade', {});

```

To specify the the default implementation for any block, simply use the keyword 'default', as in the following example.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

```

```

cfg.forEach( './Subsystem/MinMax', ...

'built-in/MinMax', {}, ...

'default');

```

Refer to "Summary of Block Implementations" in the Simulink® HDL Coder™ documentation for a complete listing of supported blocks and their implementations.

#### **Compatibility Considerations**

In previous releases, control files specified block implementations using package.class syntax. For example, the following control file specifies the cascade implementation for Sum blocks, using package.class syntax.

```

function cfg = controlFile

cfg = hdlnewcontrol(mfilename);

cfg.forEach('*',...

'built-in/Sum', {},...

'hdldefaults.SumCascadeHDLEmission', {});

```

The coder continues to support control files that use package.class syntax. However, we strongly recommend that you convert existing control files to the new syntax. To convert an existing control file:

- Open a model that is linked to the control file.

- Open the Configuration Parameters dialog box and select the HDL Coder pane.

- Click Generate to generate HDL code for the model. The code generation

process updates in-memory information that will be written to your

updated control file.

- In the **Code generation control file** subpane, click **Save**. This overwrites the existing control file. The updated control file will use the new syntax.

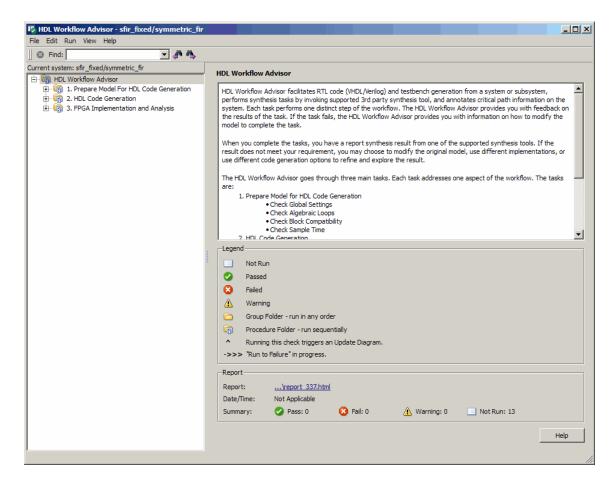

#### **HDL Workflow Advisor**

The HDL Workflow Advisor is a GUI tool that supports all stages of the FPGA design process, including the following:

- Checking the Simulink model for HDL code generation compatibility

- HDL code and test bench generation

- Synthesis and timing analysis through integration with third-party synthesis tools (r2010a supports Xilinx® ISE)

- Back annotation of the Simulink model with critical path and other information obtained during synthesis.

The following figure shows the top-level HDL Workflow Advisor window.

See "Using the HDL Workflow Advisor" for further information.

## Additional Simulink Blocks Supported for HDL Code Generation

The coder now supports the blocks listed in the following table for HDL code generation.

| Block                                                                                    | Notes                                                                                                    |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| simulink/Additional Math & Discrete/Additional<br>Discrete/Unit Delay Enabled Resettable |                                                                                                          |

| simulink/Additional Math & Discrete/Additional Discrete/Unit Delay Resettable            |                                                                                                          |

| simulink/Math Operations/Trigonometric Function                                          | See also "CORDIC Algorithm<br>Supported for Trigonometric<br>Functions (sin, cos, sincos)" on page<br>9. |

| Signal Processing Blockset/Signal Operations/Repeat                                      |                                                                                                          |

| Communications Blockset/Digital Baseband Modulation/PM:                                  |                                                                                                          |

| • PSK Modulators (BPSK,M-PSK,QPSK)                                                       |                                                                                                          |

| • PSK Demodulators (BPSK,M-PSK,QPSK)                                                     |                                                                                                          |

| Communications Blockset/Interleaving/Convolutional:  • Convolutional Interleaver         | "Convolutional Interleaver and<br>Deinterleaver Block Requirements<br>and Restrictions"                  |

| Convolutional Deinterleaver                                                              |                                                                                                          |

| Communications Blockset/Error Detection and<br>Correction/Convolutional/Viterbi Decoder  | "Viterbi Decoder Block Requirements and Restrictions"                                                    |

"Summary of Block Implementations" in the Simulink HDL Coder documentation gives a complete listing of blocks that the coder supports for HDL code generation.

# CORDIC Algorithm Supported for Trigonometric Functions (sin, cos, sincos)

The Simulink Trigonometric Function block now supports the CORDIC algorithm for the sin,cos, and sincos functions.

Simulink HDL Coder HDL Coder now supports HDL code generation for the Trigonometric Function block for the sin,cos, and sincos functions. To generate HDL code for one these functions, select the Trigonometric Function block, you must set the **Approximation method** parameter to CORDIC.

See also "Trigonometric Function Block Requirements and Restrictions" in the Simulink HDL Coder documentation.

### **Option to Minimize Generation of Clock Enables**

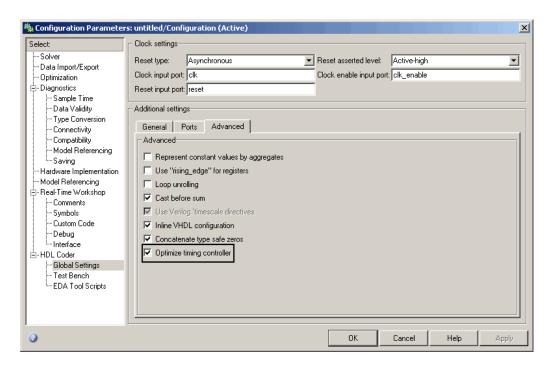

The new **Minimize clock enables** options lets you suppress generation of clock enable logic for single-rate designs, wherever possible. If your target device does not have registers with clock enables, you may want to consider selecting this option.

You can also use the command-line property MinimizeClockEnable to suppress generation of clock enable logic.

See also "Minimize clock enables" in the Simulink HDL Coder documentation.

# VHDLArchitectureName Property Supports Specification of Architecture Name

The new VHDLArchitectureName property lets you specify the architecture name for generated HDL code. The default architecture name is 'rtl'.

# VHDLLibraryName Property Supports Specification of Target Library

The new VHDLLibraryName property lets you specify the name of the target library for generated HDL code. The default target library name is 'work'.

### **Output Pipelining Now Supported for Subsystems**

The coder now supports the OutputPipeline property for subsystems.

For detailed information, see "OutputPipeline" in the Simulink HDL Coder documentation. "Distributed Pipeline Insertion for Embedded MATLAB Function Blocks" in the Simulink HDL Coder documentation.

### **Distributed Pipelining Now Supported for Subsystems**

In the previous release, the coder supported the DistributedPipelining property for Embedded MATLAB® Function blocks or Stateflow® charts within a subsystem.. In R2010a, the coder also supports this property for any subsystem.

For detailed information, see "Distributed Pipeline Insertion for Embedded MATLAB Function Blocks" in the Simulink HDL Coder documentation.

## CSD and Factored CSD Optimizations for Constant Multiplications

You can now specify Canonic Signed Digit (CSD) and Factored Canonic Signed Digit (FCSD) techniques to optimize multiplication operations involving constants.

The ConstMultiplierOptimization implementation supports CSD and FCSD optimizations for the following blocks:

- Gain

- Stateflow chart

- Truth Table

- Embedded MATLAB

See also "ConstMultiplierOptimization".

### **Enhanced Gain Block Support**

The coder now supports the following for HDL code generation for the Gain block:

- Use of Matrix (k\*u) (u vector) mode for the Gain parameter.

- If you specify the implementation parameter ConstMultiplierOptimization, 'auto') for the Gain block, the coder automatically selects CSD or FCSD implementations based on the number of required adders.

### FIR Decimation Filter Supports Distributed Arithmetic Architecture

The code now supports distributed arithmetic (DA) filter implementations for the dspmlti4/FIR Decimation block. See "Distributed Arithmetic Implementation Parameters for Digital Filter Blocks" in the Simulink HDL Coder documentation for details.

#### Serial, Partly Serial and Cascade Serial Architectures Supported for FIR Filter Implementations

The coder now supports serial, partly serial and cascade serial architectures for the following blocks:

- dsparch4/Digital Filter (FIR structures only)

- simulink/Discrete/Discrete FIR Filter

- dspmlti4/FIR Decimation

You can specify serial architectures using the SerialPartition and ReuseAccum implementation parameters. See "Speed vs. Area Optimizations for FIR Filter Implementations" for further information.]

# InstancePostfix Property Allows Specification of Extension to Postfix String

In R2010a, the coder supports the InstancePostfix. InstancePostfix lets you specify a string appended after component instance names in generated code. The default value for InstancePostfix is ''(no postfix added).

### Version 1.6 (R2009b) Simulink HDL Coder Software

This table summarizes what's new in Version 1.6 (R2009b):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations                                                | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | Yes—Details labeled<br>as Compatibility<br>Considerations,<br>below. See also<br>Summary. | None                             | None                                    |

New features and changes introduced in this version are:

- "Triggered Subsystems Support for HDL Code Generation" on page 14

- "Stateflow Events Support for HDL Code Generation" on page 14

- "Support for Global Oversampling Clock" on page 14

- "Test Bench GUI Reorganized" on page 15

- "MATLAB Editor Supports VHDL and Verilog Syntax Highlighting" on page 16

- "Hyperlinked Requirements Comments Included in HTML Code Generation Reports" on page 16

- "HTML Code Generation Report from Root-Level Model Supported" on page 16

- "Generation of Simulink Model for Cosimulation of Generated HDL Code" on page 17

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 17

- "New hdldemolib Block Supports Streaming FFT" on page 18

- "Algebraic Loops Disallowed for HDL Code Generation" on page 18

- "DUT Argument Required for checkhdl and makehdl Commands" on page 18

- "AddClockEnablePort Implementation Parameter for RAM Blocks Deprecated" on page 19

- "Additional Lookup Table Blocks Supported" on page 20

- "Discrete FIR Filter Supports Distributed Arithmetic Architecture" on page 21

- "Generation of Multicycle Path Constraint Information" on page 21

- "Biquad Filter and Digital Filter Blocks Support Complex Input Data and Coefficients" on page 22

- "Support for Adding or Removing HDL Configuration Component" on page 23

### Triggered Subsystems Support for HDL Code Generation

The coder now supports HDL code generation for triggered subsystems. See "Code Generation for Enabled and Triggered Subsystems" in the Simulink HDL Coder documentation for further information.

### **Stateflow Events Support for HDL Code Generation**

The coder now supports a single input event and unlimited output events in Stateflow charts. for further information, see "Using Input and Output Events" in the Simulink HDL Coder documentation.

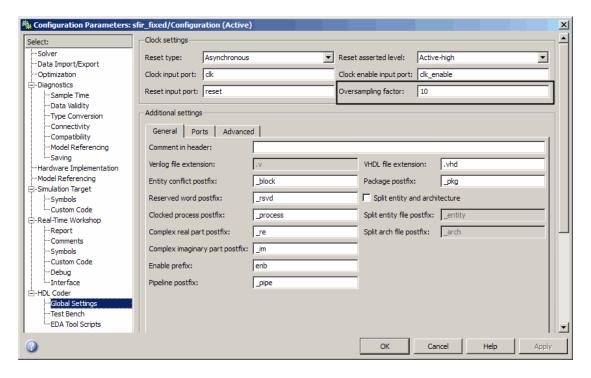

### **Support for Global Oversampling Clock**

You can now generate global clock logic that allows you to integrate your DUT into a larger system easily, without using Upsample or Downsample blocks.

To generate global clock logic, you specify an *oversampling factor*. The oversampling factor expresses the desired rate of the global oversampling clock as a multiple of the base rate of the model. When you specify an oversampling factor, the coder generates the global oversampling clock. Then, it derives the required timing signals from the clock signal. Generation of the

global oversampling clock affects only generated HDL code. The clock does not affect the simulation behavior of your model.

You can specify the desired factor as the **Oversampling factor** option in the **Clock settings** section of the **Global Settings** pane of the Configuration Parameters dialog. The following figure shows the option. Alternatively, you can set the command-line property 'Oversampling'.

See "Generating a Global Oversampling Clock" in the Simulink HDL Coder documentation for further information.

#### **Test Bench GUI Reorganized**

The new **Testbench generation output** section of the GUI contains three new options:

- **HDL test bench**: Selecting this option enables generation of an HDL test bench, and also enables all options in the **Configuration** section of the **Test Bench** pane.

- Cosimulation blocks: Selecting this option enables generation of a model containing HDL Cosimulation block for use in testing the DUT. Selecting this option also enables all options in the Configuration section of the Test Bench pane.

- **Cosimulation model for use with**: This option enables generation of a model containing an HDL Cosimulation block for use in testing with a selected cosimulation tool. Selecting this option also enables all options in the **Configuration** section of the **Test Bench** pane.

To configure test bench options and generate test bench code, select one or more of the options of the **Testbench generation output** section. If you deselect all three options of the **Testbench generation output** section, the coder disables all options in the **Configuration** section of the **Test Bench** pane.

# MATLAB Editor Supports VHDL and Verilog Syntax Highlighting

The MATLAB Editor now supports syntax highlighting for VHDL and Verilog code. See "Highlighting Syntax to Help Ensure Correct Entries" in the MATLAB documentation for further information on syntax highlighting.

# Hyperlinked Requirements Comments Included in HTML Code Generation Reports

The coder now renders requirements comments as hyperlinked comments within generated HTML code generation reports. See "Requirements Comments and Hyperlinks" in the Simulink HDL Coder documentation for further information.

### HTML Code Generation Report from Root-Level Model Supported

In previous releases, the coder did not support generation of HTML code generation reports from the root-level model. R2009b removes this restriction.

You can now generate reports for the root-level model as well as for subsystems, blocks, Stateflow charts, or Embedded MATLAB blocks.

### Generation of Simulink Model for Cosimulation of Generated HDL Code

The coder now supports generation of a Simulink model configured for:

- Simulink simulation of your design

- Cosimulation of your design with an HDL simulator

The generated model includes a behavioral model of your design and a corresponding HDL Cosimulation block, configured to cosimulate the design using EDA Simulator Link<sup>TM</sup>. You can generate an HDL Cosimulation block for either of the following:

- EDA Simulator Link for use with Mentor Graphics®ModelSim®

- EDA Simulator Link for use with Cadence Incisive®

See "Generating a Simulink Model for Cosimulation with an HDL Simulator" for further information.

### Additional Simulink Blocks Supported for HDL Code Generation

The coder now supports the blocks listed in the following table for HDL code generation.

| Block                                            | Implementation                                |

|--------------------------------------------------|-----------------------------------------------|

| hdldemolib/HDL Streaming FFT                     | hdldefaults.FFT                               |

| Ports & Subsystems/Trigger                       | hdldefaults.TriggerPort                       |

| simulink/Discrete/Discrete FIR Filter            | hdldefaults.DiscreteFIRFilterHDLInstantiation |

| simulink/Lookup Tables/Direct Lookup Table (n-D) | hdldefaults.DirectLookupTable                 |

| Block                                     | Implementation            |

|-------------------------------------------|---------------------------|

| simulink/Lookup Tables/Lookup Table (n-D) | hdldefaults.LookupTableND |

| simulink/Lookup Tables/Prelookup          | hdldefaults.PreLookup     |

"Summary of Block Implementations" in the Simulink HDL Coder documentation gives a complete listing of blocks that the coder supports for HDL code generation.

#### **New holdemolib Block Supports Streaming FFT**

The new hdldemolib/HDL Streaming FFT block supports a Radix-2 DIF streaming FFT algorithm.

See "HDL Streaming FFT" in the Simulink HDL Coder documentation for details.

### Algebraic Loops Disallowed for HDL Code Generation

The coder now checks for algebraic loops during the compatibility checking phase of the code generation process. If makehdl detects an algebraic loop inside the DUT, the coder displays an error message and ends the code generation process.

#### **Compatibility Considerations**

Restructure any of your models that contain algebraic loops such that algebraic loops do not occur. It is also good practice to set the **Algebraic loop** diagnostic in the **Diagnostics** pane of the Configuration Parameters dialog box to error.

### DUT Argument Required for checkhall and makehall Commands

R2009b requires that calls to the following functions must specify the device under test (DUT):

• checkhdl

#### • makehdl

When you call checkhdl or makehdl, specify the DUT as the initial argument to these functions, as in the following example:

```

makehdl('sfir_fixed/symmetric_fir','TargetLanguage', 'Verilog');

```

As in previous releases, you can specify the DUT in any of the following forms:

- bdroot: the current model.

- 'modelname': an explicitly specified model.

- 'modelname/subsys': explicitly specified path to a subsystem.

- gcb: the currently selected subsystem

This requirement avoids certain ambiguities that occurred in calls to checkhol or makehol that did not pass in an explicit DUT argument.

In R2009b, the coder displays a warning if it encounters a call to checkhdl or makehdl without the DUT argument. In future releases, the coder will generate an error if it encounters a call to either of these functions without the DUT argument.

See also the checkhdl and makehdl function reference pages in the Simulink HDL Coder documentation.

#### **Compatibility Considerations**

If your MATLAB files contain any calls to checkhdl or makehdl that do not specify the DUT, modify them to pass in the DUT as the initial argument.

# AddClockEnablePort Implementation Parameter for RAM Blocks Deprecated

The AddClockEnablePort implementation parameter for the Dual Port RAM and Single Port RAM blocks is deprecated. The coder issues an error message if it detects a reference to AddClockEnablePort in a control file.

#### **Compatibility Considerations**

If you use the AddClockEnablePort in a control file to suppress to generation of a clock enable signal for RAM blocks:

- Remove all references to AddClockEnablePort from your control files.

- Use the generic RAM templates instead. The generic RAM templates do not use a clock enable signal for RAM structures. The generic RAM template implements clock enable with logic in a wrapper around the RAM. Consider the generic RAM style if

- Your synthesis tool does not support RAM structures with a clock enable

- Your synthesis tool cannot map generated HDL code to FPGA RAM resources.

To learn how to use generic style RAM for your design, see the new Getting Started with RAM and ROM in Simulink demo. To open the demo, type the following command at the MATLAB prompt:

hdlcoderramrom

#### **Additional Lookup Table Blocks Supported**

The coder now supports the following lookup table (LUT) blocks for HDL code generation:

- simulink/Lookup Tables/Lookup Table (n-D)

- simulink/Lookup Tables/Prelookup

- simulink/Lookup Tables/Direct Lookup Table (n-D)

Expanded LUT functionality supported for these blocks includes:

- Tables of two dimensions

- Prelookup

- Interpolation

- Extrapolation

See "Using Lookup Table Blocks" in the Simulink HDL Coder documentation for details.

### Discrete FIR Filter Supports Distributed Arithmetic Architecture

The code now supports distributed arithmetic (DA) filter implementations for the Discrete FIR Filter block. See "Distributed Arithmetic Implementation Parameters for Digital Filter Blocks" in the Simulink HDL Coder documentation for details.

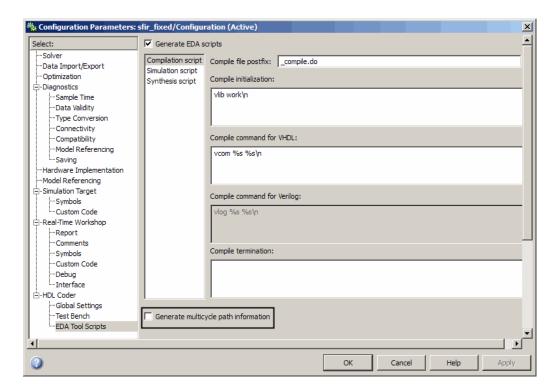

### **Generation of Multicycle Path Constraint Information**

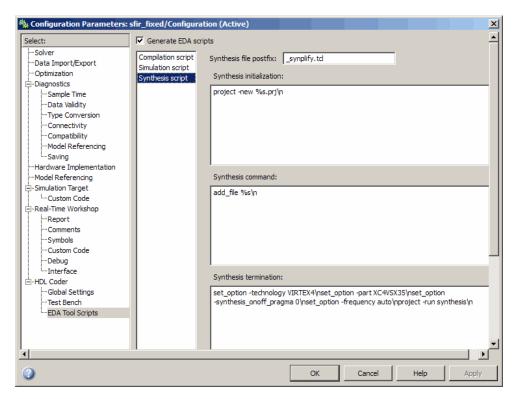

The coder now supports generation of a text file that reports multicycle path constraint information. You can use this information with your synthesis tool.

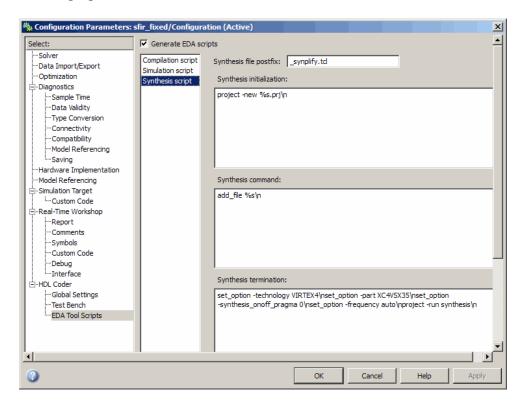

To generate the file, select the **Generate multicycle path information** option in the **EDA Tool Scripts** pane of the Configuration Parameters dialog box. The following figure shows this option.

To generate a multicycle path constraint information file at the command line, set the MulticyclePathInfo property as shown in the following example.

```

makehdl(gcb,'MulticyclePathInfo', 'on');

```

See "Generating Multicycle Path Information Files" in the Simulink HDL Coder documentation for detailed information.

# Biquad Filter and Digital Filter Blocks Support Complex Input Data and Coefficients

The Biquad Filter and Digital Filter blocks now support complex input data and coefficients for all filter structures except decimators and interpolators.

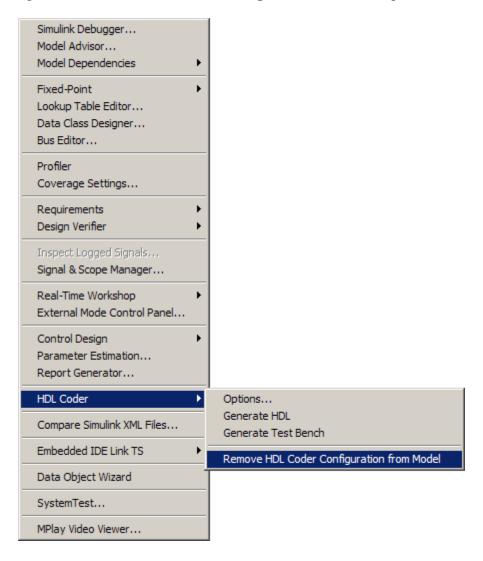

# Support for Adding or Removing HDL Configuration Component

The **HDL Coder** submenu of the **Tools** menu now supports addition or removal of the HDL Coder configuration component of a model. The following figure shows the **Remove HDL Configuration to Model** option.

See "Adding and Removing the HDL Configuration Component" Simulink HDL Coder documentation for more information.

### Version 1.5 (R2009a) Simulink HDL Coder Software

This table summarizes what's new in Version 1.5 (R2009a):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations                                                | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | Yes—Details labeled<br>as Compatibility<br>Considerations,<br>below. See also<br>Summary. | None                             | None                                    |

New features and changes introduced in this version are:

- "hdlsupported Library Reorganized" on page 26

- "HTML Code Generation Report" on page 26

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 28

- "Enabled Subsystems Supported for HDL Code Generation" on page 29

- "New Default HDL Implementations for Selected Blocks" on page 30

- "New HDL Implementations for Selected Blocks" on page 31

- "Distributed Arithmetic Implementations for the Digital Filter Block" on page 32

- "Complex Data Supported for the Digital Filter Block" on page 32

- "Requirements Comments Included in Generated Code" on page 33

- "Restriction on fi and fimath Rounding Modes in Embedded MATLAB Function Block Removed" on page 33

- "Restriction on for Loop Increment in Embedded MATLAB Function Block Removed" on page 34

- "Generic RAM Template Supports RAM Without a Clock Enable Signal" on page 34

• "Generating ROM with Lookup Table and Unit Delay Blocks" on page 35

### hdlsupported Library Reorganized

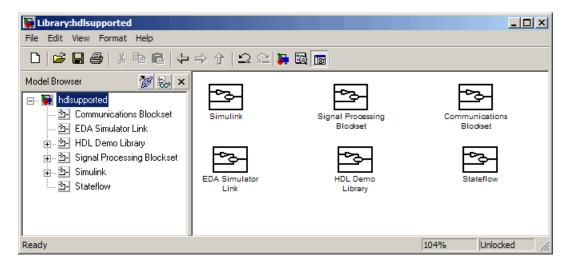

The hdlsupported.mdl block library has been reorganized into several sublibraries to help you locate the HDL-compatible blocks you need more easily. The following figure shows the top-level view of the hdlsupported.mdl library.

The set of supported blocks will change in future releases of the coder. To keep the hdlsupported.mdl current, you should rebuild the library each time you install a new release. See "Supported Blocks Library" in the Simulink HDL Coder documentation for further information.

#### **HTML Code Generation Report**

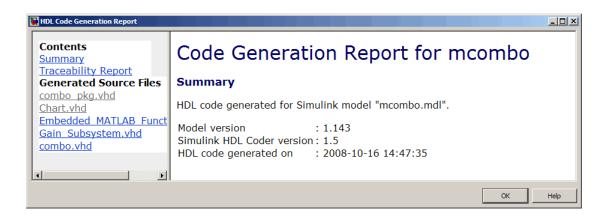

To help you navigate more easily between generated code and your source model, the coder provides a *traceability* option that lets you generate reports from either the GUI or the command line. When you enable traceability, the coder creates and displays an HTML code generation report during the code generation process. The following figure shows the top-level page of a typical report.

The report comprises several sections:

- The **Summary** section lists version and date information.

- The Generated Source Files table contains hyperlinks to that let you view generated HDL code in a MATLAB Web browser window. This view of the code includes hyperlinks that let you view the blocks or subsystems from which the code was generated. You can click the names of source code files generated from your model to view their contents in a MATLAB Web browser window. The report supports two types of linkage between the model and generated code:

- Code-to-model hyperlinks within the displayed source code let you view the blocks or subsystems from which the code was generated. Click on the hyperlinks to view the relevant blocks or subsystems in a Simulink model window.

- Model-to-code linkage lets you view the generated code for any block in the model. To highlight a block's generated code in the HTML report, right-click the block and select HDL Coder > Navigate to Code from the context menu.

- The Traceability Report allows you to account for Eliminated / Virtual Blocks that are untraceable, versus the listed Traceable Simulink Blocks / Stateflow Objects / Embedded MATLAB Scripts, providing a complete mapping between model elements and code.

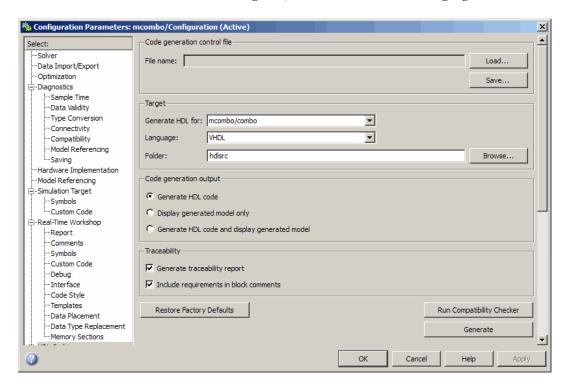

To enable generation of the HTML code generation report, select **Generate traceability report** in the **HDL Coder** pane of the Configuration Parameters dialog box, as shown in the following figure.

See "Creating and Using a Code Generation Report" in the Simulink HDL Coder documentation for further information.

### Additional Simulink Blocks Supported for HDL Code Generation

The coder now supports the blocks listed in the following table for HDL code generation.

| Block                                                                                                     | Implementation(s)     |

|-----------------------------------------------------------------------------------------------------------|-----------------------|

| simulink/Additional Math & Discrete/<br>Additional Math: Increment -<br>Decrement/Decrement Real World    | default               |

| simulink/Additional Math & Discrete/<br>Additional Math: Increment -<br>Decrement/Increment Real World    | default               |

| simulink/Additional Math & Discrete/<br>Additional Math: Increment -<br>Decrement/Decrement Store Integer | default               |

| simulink/Additional Math & Discrete/<br>Additional Math: Increment -<br>Decrement/Increment Store Integer | default               |

| simulink/Discontinuties/Saturation Dynamic                                                                | default               |

| simulink/Math Operations/Reciprocal Sqrt                                                                  | default, SqrtFunction |

|                                                                                                           | RecipSqrtNewton       |

|                                                                                                           | SqrtBitset            |

|                                                                                                           | SqrtNewton            |

| Signal Routing/Go To                                                                                      | default               |

| Signal Routing/From                                                                                       | default               |

| dsparch4/Biquad Filter                                                                                    | default               |

| Ports & Subsystems/Enable                                                                                 | default               |

See "Summary of Block Implementations" in the Simulink HDL Coder documentation for a complete listing of blocks that are currently supported for HDL code generation.

# **Enabled Subsystems Supported for HDL Code Generation**

The code now supports code generation for enabled subsystems, provided that they are configured as described in "Code Generation for Enabled and Triggered Subsystems" in the Simulink HDL Coder documentation.

### New Default HDL Implementations for Selected Blocks

The default HDL implementations for certain blocks has been changed. The following table lists these blocks, as well as their new default implementations and previous default implementations. All listed implementation classes belong to the package hdldefaults.

| Block                                                                                                         | Default Implementation<br>Before R2009a | New Default<br>Implementation |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------|

| simulink/Commonly Used<br>Blocks/Constant<br>simulink/Commonly Used<br>Blocks/Ground<br>dspsrcs4/DSP Constant | ConstantHDLEmission                     | Constant                      |

| simulink/Commonly Used<br>Blocks/Demux                                                                        | DemuxHDLEmission                        | Demux                         |

| simulink/Commonly Used<br>Blocks/Mux                                                                          | MuxHDLEmission                          | Mux                           |

| simulink/Commonly Used<br>Blocks/Switch                                                                       | SwitchHDLEmission                       | SwitchRTW                     |

| simulink/Math<br>Operations/Complex to<br>Real-Imag                                                           | ComplexToRealImagHDLEmission            | ComplexToRealImag             |

| simulink/Math<br>Operations/Real-Imag to<br>Complex                                                           | RealImagtoComplexHDLEmission            | RealImagtoComplex             |

See "Summary of Block Implementations" in the Simulink HDL Coder documentation for a complete listing of blocks that are currently supported for HDL code generation.

#### **Compatibility Considerations**

If your models use default HDL block implementations for the affected blocks, the coder now defaults to the new implementations. The new implementations

are compatible with the previous implementations and will produce identical results.

The older implementations for the listed blocks will be supported for a limited number of future releases. If your control files explicitly reference the previous default implementation for any of the affected blocks, the coder will continue to use the referenced implementation. You should consider removing or changing such references in your control files to use the new implementations.

#### **New HDL Implementations for Selected Blocks**

A number of HDL block implementations have been changed. The following table lists these blocks, as well as their new implementations and the earlier implementations that they replace. All listed implementation classes belong to the package hdldefaults.

| Block                                                                                       | Implementation Before R2009a | New Implementation |

|---------------------------------------------------------------------------------------------|------------------------------|--------------------|

| simulink/Math<br>Operations/MinMax<br>dspstat3/Maximum<br>dspstat3/Minimum                  | MinMaxCascadeHDLEmission     | MinMaxCascade      |

| simulink/Commonly Used<br>Blocks/Sum<br>simulink/Math Operations/Sum of<br>Elements         | SumTreeHDLEmission           | SumTree            |

| simulink/Commonly Used<br>Blocks/Product<br>simulink/Math<br>Operations/Product of Elements | ProductTreeHDLEmission       | ProductTree        |

| simulink/Commonly Used<br>Blocks/Sum<br>simulink/Math Operations/Sum of<br>Elements         | SumCascadeHDLEmission        | SumCascade         |

| simulink/Commonly Used<br>Blocks/Product<br>simulink/Math<br>Operations/Product of Elements | ProductCascadeHDLEmission    | ProductCascade     |

See "Summary of Block Implementations" in the Simulink HDL Coder documentation for a complete listing of blocks that are currently supported for HDL code generation.

#### **Compatibility Considerations**

The new implementations are compatible with the previous implementations and will produce identical results.

The older implementations for the listed blocks will be supported for a limited number of future releases. If your control files explicitly reference the previous implementation for any of the affected blocks, the coder will continue to use the referenced implementation. You should consider removing or changing such references in your control files to use the new implementations.

### Distributed Arithmetic Implementations for the Digital Filter Block

Distributed Arithmetic (DA) is a widely used technique for implementing sum-of-products computations without using multipliers. DA distributes multiply and accumulate operations across shifters, lookup tables (LUTs) and adders in such a way that conventional multipliers are not required. The coder now supports DA implementations for the following FIR structures of the Digital Filter block:

- dfilt.dffir

- dfilt.dfsymfir

- dfilt.dfasymdir

See "Block Implementation Parameters" in the Simulink HDL Coder documentation for further information.

### Complex Data Supported for the Digital Filter Block

The coder supports complex coefficients and complex input signals for fully parallel FIR and CIC filter structures of the Digital Filter block. In many cases, you can use complex data and complex coefficients in combination. The following table shows the filter structures that support complex data and/or coefficients, and the permitted combinations.

| Filter Structure | Complex<br>Data | Complex<br>Coefficients | Both Complex<br>Data<br>and Coefficients |

|------------------|-----------------|-------------------------|------------------------------------------|

| dfilt.dffir      | Y               | Y                       | Y                                        |

| dfilt.dfsymfir   | Y               | Y                       | Y                                        |

| dfilt.dfasymfir  | Y               | Y                       | Y                                        |

| dfilt.dffirt     | Y               | Y                       | Y                                        |

| mfilt.cicdecim   | Y               | N/A                     | N/A                                      |

| mfilt.cicinterp  | Y               | N/A                     | N/A                                      |

| mfilt.firdecim   | Y               | Y                       | N                                        |

| mfilt.firinterp  | Y               | Y                       | N                                        |

See "Blocks That Support Complex Data" for further information on how the coder supports use of complex data.

### **Requirements Comments Included in Generated Code**

Requirements that you assign to Simulink blocks are now automatically included as comments in generated code. See the  $Simulink^{®}$  Verification and  $Validation^{TM}$  User's Guide in the Simulink HDL Coder documentation for further information on requirements comments.

#### Restriction on fi and fimath Rounding Modes in Embedded MATLAB Function Block Removed

In previous releases, the coder did not support the convergent and round modes for the fi and fimath functions in Embedded MATLAB Function blocks.

This restriction has been removed; the coder now supports all fi and fimath rounding modes.

See also "Generating HDL Code with the Embedded MATLAB Function Block" in the Simulink HDL Coder documentation.

## Restriction on for Loop Increment in Embedded MATLAB Function Block Removed

In previous releases, the use of for loops with an increment other than 1 in an Embedded MATLAB Function Block was not supported for HDL code generation.

This restriction has been removed. The coder now allows use of any increment in a for loop in an Embedded MATLAB Function Block.

See also "Generating HDL Code with the Embedded MATLAB Function Block" in the Simulink HDL Coder documentation.

## Generic RAM Template Supports RAM Without a Clock Enable Signal

The hdldemolib library provides three type of RAM blocks:

- Dual Port RAM

- Simple Dual Port RAM

- Single Port RAM

These blocks (see "RAM Blocks" in the Simulink HDL Coder documentation) implement RAM structures using HDL templates that include a clock enable signal.

However, some synthesis tools do not support RAM inference with a clock enable. As an alternative, the coder now provides a generic style of HDL templates that do not use a clock enable signal for the RAM structures. The generic RAM template implements clock enable with logic in a wrapper around the RAM.

You may want to use the generic RAM style if your synthesis tool does not support RAM structures with a clock enable, and cannot map generated HDL code to FPGA RAM resources. To learn how to use generic style RAM for your design, see the new Getting Started with RAM and ROM in Simulink demo. To open the demo, type the following command at the MATLAB prompt:

hdlcoderramrom

## Generating ROM with Lookup Table and Unit Delay Blocks

Simulink HDL Coder does not provide a ROM block, but you can easily build one using basic Simulink blocks. The new Getting Started with RAM and ROM in Simulink demo includes an example in which a ROM is built using a Lookup Table block and a Unit Delay block. To open the demo, type the following command at the MATLAB prompt:

hdlcoderramrom

## Version 1.4 (R2008b) Simulink HDL Coder Software

This table summarizes what's new in Version 1.4 (R2008b):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations                                                | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | Yes—Details labeled<br>as Compatibility<br>Considerations,<br>below. See also<br>Summary. | Bug Reports                      | No                                      |

New features and changes introduced in this version are:

- "New hdldemolib Blocks Support FFT, HDL Counter, and Bitwise Operators" on page 37

- "Additional Simulink Blocks Supported for HDL Code Generation" on page 39

- "Complex Signals Supported for Additional Blocks" on page 39

- "Code Annotation Support" on page 40

- "New Constant Block Implementation Indicates Hi-Z or Unknown States" on page 41

- "New Test Bench Reference Postfix Option" on page 41

- $\bullet\,$  "New Default HDL Implementations for Selected Blocks" on page  $43\,$

- "Default Entity Conflict Postfix Changed" on page 44

- "New DistributedPipelining Implementation Parameter for Embedded MATLAB Function Blocks and Stateflow Charts" on page 44

- "Coefficient Multiplier Optimization for Digital Filter, FIR Decimation, and FIR Interpolation Filters" on page 45

- "hdlnewblackbox Function Generates Black Box Control Statements" on page 46

- "hdlnewcontrolfile Function Optionally Returns Result to String" on page 47

- "-novopt Flag Added to Default Simulation Command in Generated Compilation Scripts" on page 47

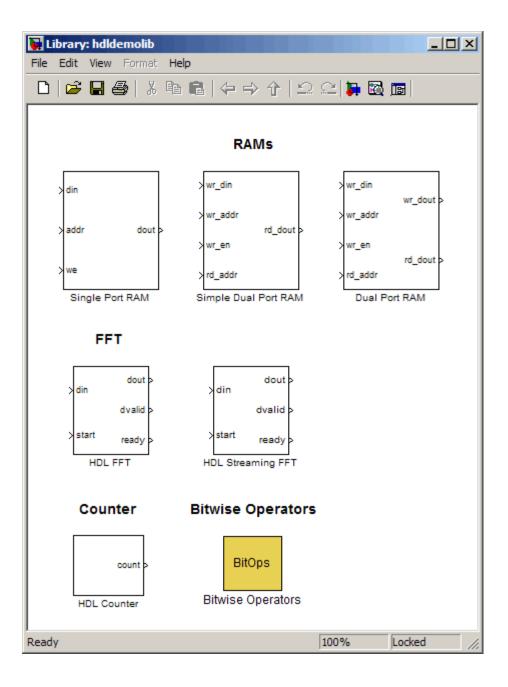

## New holdemolib Blocks Support FFT, HDL Counter, and Bitwise Operators

The hdldemolib library now includes HDL-specific block implementations supporting simulation and code generation for:

- Counter with count-limited and free-running modes (see "HDL Counter" in the Simulink HDL Coder documentation)

- Minimum resource FFT (see "HDL FFT" in the Simulink HDL Coder documentation)

- Bitwise operations, including bit slice, bit reduction, bit concatenation, bit shift, and bit rotation (see "Bitwise Operators" in the Simulink HDL Coder documentation)

The following figure shows the hdldemolib library window. See "The hdldemolib Block Library" in the Simulink HDL Coder documentation for more information about the library.

## Additional Simulink Blocks Supported for HDL Code Generation

The coder now supports the following blocks for HDL code generation:

- Signal Processing Blockset/Multirate Filters/CIC Interpolation

- Signal Processing Blockset/Multirate Filters/FIR Interpolation (See the demo "Digital Down Converter for HDL Code Generation" for an example of the use of this block.)

- Signal Processing Blockset/Filtering /Adaptive Filters/LMS Filter

(See the demo "Adaptive Noise Canceler with LMS Filter" for an example of the use of this block.)

- simulink/Logic and Bit Operations/Extract Bits

- simulink/Math Operations/Math Function (now supports hermitian, and transpose functions for HDL code generation)

- simulink/Model-Wide Utilities/DocBlock

- Stateflow Truth Table

In addition, several HDL-specific block implementations have been added to the hdldemolib library. See "New hdldemolib Blocks Support FFT, HDL Counter, and Bitwise Operators" on page 37.

See "Summary of Block Implementations" in the Simulink HDL Coder documentation for a complete listing of blocks that are currently supported for HDL code generation.

## **Complex Signals Supported for Additional Blocks**

In the previous release, the coder introduced support for use of complex signals with a limited set of blocks. In R2008b, the coder supports complex signals for these additional blocks:

- dspadpt3/LMS Filter

- dspsigattribs/Frame Conversion

- dspsigops/Delay (DSPDelayHDLEmission implementation)

- hdldemolib/Dual Port RAM

- hdldemolib/Simple Dual Port RAM

- hdldemolib/Single Port RAM

- hdldemolib/HDL FFT

- simulink/Commonly Used Blocks/Relational Operator (~= and == operators only)

- simulink/Discrete/Memory

- simulink/Discrete/Zero-Order Hold

- simulink/Logic and Bit Operations/Compare To Constant

- simulink/Logic and Bit Operations/Compare To Zero

- simulink/Lookup Tables/Lookup Table (LookupHDLInstantiation implementation)

- simulink/Math Operations/Assignment

- simulink/Math Operations/Math Function (hermitian, transpose)

- simulink/Signal Attributes/Signal Specification

See "Blocks That Support Complex Data" in the Simulink HDL Coder documentation for a complete listing of blocks that support complex signals.

### **Code Annotation Support**

The coder now lets you add text annotations to generated code, in the form of comments. There are two ways to add annotations to your code:

- Enter text directly on the block diagram as Simulink annotations.

- Place a DocBlock at the desired level of your model and enter text comments.

See "Annotating Generated Code with Comments and Requirements" in the Simulink HDL Coder documentation for further information.

## New Constant Block Implementation Indicates Hi-Z or Unknown States

The coder now supports an implementation for the built-in/Constant block (hdldefaults.ConstantSpecialHDLEmission), which you can use to indicate when a constant signal is in high-impedance ('Z') or unknown ('X') state. The implementation provides the {Value} parameter to indicate the state, as follows:

- {Value, 'Z'}: If the signal is in a high-impedance state, the Constant block emits the character 'Z' for each bit in the signal. For example, for a 4-bit signal, 'ZZZZ' would be emitted.

- {Value, 'Z'} is the default value for this implementation.

- {Value, 'X'}: If the signal is in an unknown state, the Constant block emits the character 'X' for each bit in the signal. For example, for a 4-bit signal, 'XXXX' would be emitted.

hdldefaults.ConstantSpecialHDLEmission does not support the double data type.

See also "Blocks with Multiple Implementations" in the Simulink HDL Coder documentation.

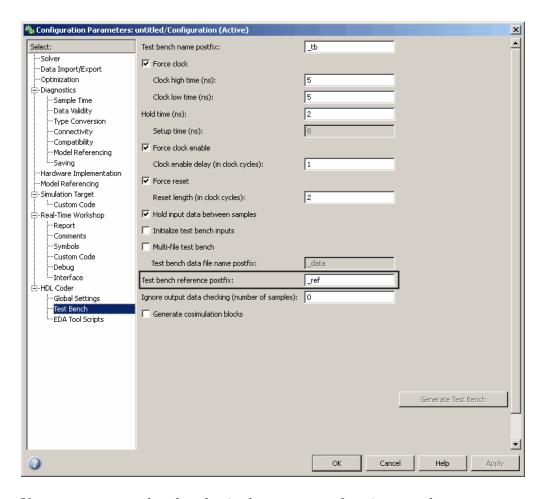

### **New Test Bench Reference Postfix Option**

The new **Test bench reference postfix** option (shown in the following figure) lets you customize the names of reference signals generated in test bench code by specifying a string to be appended to reference signal names. The default string is '\_ref'.

If you generate test bench code via the makehdltb function, use the Testbenchreferencepostfix property (see TestBenchReferencePostFix in the in the Simulink HDL Coder documentation) to specify the postfix string.

## New Default HDL Implementations for Selected Blocks

The default HDL implementations for certain blocks has been changed. The following table lists these blocks, as well as their new default implementations and previous default implementations. All listed implementation classes belong to the package hdldefaults.

| Block                                                 | Default Implementation<br>Before Release R2008b | New Default<br>Implementation |

|-------------------------------------------------------|-------------------------------------------------|-------------------------------|

| simulink/Commonly Used<br>Blocks/Data Type Conversion | DataTypeConversionHDLEmission                   | DataTypeConversionRTW         |

| simulink/Commonly Used<br>Blocks/Product              | ProductLinearHDLEmission                        | ProductRTW                    |

| simulink/Math<br>Operations/Divide                    | ProductLinearHDLEmission                        | ProductRTW                    |

| simulink/Math<br>Operations/Product of<br>Elements    | ProductLinearHDLEmission                        | ProductRTW                    |

| simulink/Commonly Used<br>Blocks/Sum                  | SumLinearHDLEmission                            | SumRTW                        |

| simulink/Math<br>Operations/Add                       | SumLinearHDLEmission                            | SumRTW                        |

| simulink/Math<br>Operations/Sum of Elements           | SumLinearHDLEmission                            | SumRTW                        |

| simulink/Math<br>Operations/Subtract                  | SumLinearHDLEmission                            | SumRTW                        |

| simulink/Commonly Used<br>Blocks/Unit Delay           | UnitDelayHDLEmission                            | UnitDelayRTW                  |

| simulink/Math<br>Operations/MinMax                    | MinMaxTreeHDLEmission                           | MinMaxTree                    |

| dspstat3/Maximum                                      | MinMaxTreeHDLEmission                           | MinMaxTree                    |

| dspstat3/Minimum                                      | MinMaxTreeHDLEmission                           | MinMaxTree                    |

#### **Compatibility Considerations**

If your models use default HDL block implementations for the affected blocks, the coder will now default to the new implementations. The new implementations are compatible with the previous implementations and will produce identical results.

The older implementations for the listed blocks will be supported for a limited number of future releases. If your control files explicitly reference the previous default implementation for any of the affected blocks, the coder will continue to use the referenced implementation. You should consider removing or changing such references in your control files to use the new implementations.

### **Default Entity Conflict Postfix Changed**

The default value for the **Entity conflict postfix** property (and the corresponding CLI property, EntityConflictPostfix) has been changed from 'entity' to 'block'.

#### **Compatibility Considerations**

If your models or scripts rely on the previous default value ('\_entity') for the **Entity conflict postfix** property, you will need to explicitly set the property value to 'entity'.

### New DistributedPipelining Implementation Parameter for Embedded MATLAB Function Blocks and Stateflow Charts

In the previous release, the coder introduced automatic pipeline insertion, a special optimization for HDL code generated from Embedded MATLAB Function blocks or Stateflow charts. This optimization was enabled implicitly by specifying the {'OutputPipeline', nStages} parameter in a control file for these blocks.

In the current release, the new DistributedPipelining parameter lets you explicitly enable or disable pipeline insertion, independently from the OutputPipeline parameter. The control file listed in the following example specifies two pipeline registers, with DistributedPipelining enabled.

```

function c = pipeline_control

c = hdlnewcontrol(mfilename);

c.forEach('*',...

'eml_lib/Embedded MATLAB Function', {},...

'hdlstateflow.StateflowHDLInstantiation', {'OutputPipeline', 2, 'DistributedPipelining', 'on'});

```

The DistributedPipelining property applies only to Embedded MATLAB Function blocks or Stateflow charts within a subsystem.

For detailed information, see "Distributed Pipeline Insertion for Embedded MATLAB Function Blocks" in the Simulink HDL Coder documentation.

#### **Compatibility Considerations**

If your existing control files specified automatic pipelining implicitly using the OutputPipeline parameter, you should change your control files to specify automatic pipelining explicitly as in the following code excerpt:

```

c.forEach('*',...

'eml_lib/Embedded MATLAB Function', {},...

'hdlstateflow.StateflowHDLInstantiation', {'OutputPipeline', 2, 'DistributedPipelining', 'on'});

```

## Coefficient Multiplier Optimization for Digital Filter, FIR Decimation, and FIR Interpolation Filters

The CoeffMultipliers implementation parameter lets you specify use of canonic signed digit (CSD) or factored CSD optimizations for processing coefficient multiplier operations in code generated for certain filter blocks. Specify the CoeffMultipliers parameter in a control file using the following syntax:

• {'CoeffMultipliers', 'csd'}: Use CSD techniques to replace multiplier operations with shift and add operations. CSD techniques minimize the number of addition operations required for constant multiplication by representing binary numbers with a minimum count of nonzero digits. This decreases the area used by the filter while maintaining or increasing clock speed.

- {'CoeffMultipliers', 'factored-csd'}: Use factored CSD techniques, which replace multiplier operations with shift and add operations on prime factors of the coefficients. This option lets you achieve a greater filter area reduction than CSD, at the cost of decreasing clock speed.

- {'CoeffMultipliers', 'multipliers'} (default): Retain multiplier operations.

The coder supports CoeffMultipliers for the filter block implementations shown in the following table.

| Block                      | Implementation                               |

|----------------------------|----------------------------------------------|

| dsparch4/Digital Filter    | hdldefaults.DigitalFilterHDLInstantiation    |

| dspmlti4/FIR Decimation    | hdldefaults.FIRDecimationHDLInstantiation    |

| dspmlti4/FIR Interpolation | hdldefaults.FIRInterpolationHDLInstantiation |

See also "Block Implementation Parameters" in the Simulink HDL Coder documentation.

### hdlnewblackbox Function Generates Black Box Control Statements

The hdlnewblackbox function provides a simple way to create the control file statements that are required to generate black box interfaces for one or more subsystems.

Given a selection of one or more subsystems from your model, hdlnewblackbox returns the following as string data in the MATLAB workspace for each selected subsystem:

- A forEach call coded with the correct modelscope, blocktype, and default implementation class (SubsystemBlackBoxHDLInstantiation) arguments for the block.

- (Optional) A cell array of strings enumerating the available implementations classes for the subsystem, in package.class form.

- (Optional) A cell array of cell arrays of strings enumerating the names of implementation parameters (if any) corresponding to the implementation

classes. hdlnewblackbox does not list data types and other details of implementation parameters.

For further information, see "Generating a Black Box Interface for a Subsystem" in the Simulink HDL Coder documentation.

## hdlnewcontrolfile Function Optionally Returns Result to String

The hdlnewcontrolfile function (optionally) now can return control statements to a string variable.

To return control statements as text in the string variable t, instead of returning a control file, use the following syntax:

```

t = hdlnewcontrolfile(...)

```

See also hdlnewcontrolfile in the Simulink HDL Coder documentation.

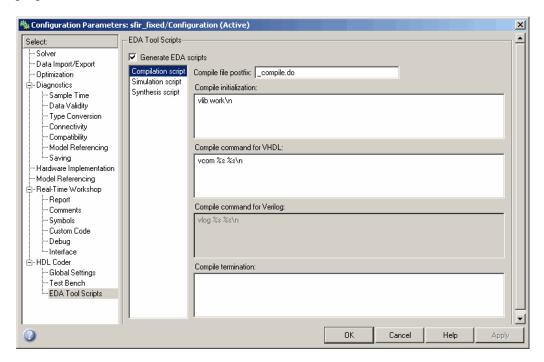

## -novopt Flag Added to Default Simulation Command in Generated Compilation Scripts

For improved operation with the ModelSim (version 6.2 and later) simulator, the default values of the HDLSimCmd property string (and the **Simulation Command** GUI option) now includes the -novopt flag, as follows:

```

'vsim -novopt work.%s\n'

```

The -novopt flag directs the ModelSim simulator not to perform optimizations that remove signals from the simulation view.

#### **Compatibility Considerations**

If you are using ModelSim 6.0 or an earlier version, you should set the HDLSimCmd property string (or the **Simulation Command** GUI option) to omit the -novopt option, as follows:

```

'vsim work.%s\n'

```

## Version 1.3 (R2008a) Simulink HDL Coder Software

This table summarizes what's new in V1.3 (R2008a):

| New Features and<br>Changes | Version<br>Compatibility<br>Considerations                                                | Fixed Bugs and<br>Known Problems | Related<br>Documentation at<br>Web Site |

|-----------------------------|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|

| Yes<br>Details below        | Yes—Details labeled<br>as Compatibility<br>Considerations,<br>below. See also<br>Summary. | Bug Reports                      | No                                      |

New features and changes introduced in this version are:

- "Complex Data Type Support" on page 49

- "Test Bench Enhancements" on page 50

- "Additional Blocks Supported for HDL Code Generation" on page 52

- "Enhanced Pipelining Support" on page 53

- "Additional RAM Blocks" on page 55

- "Enhanced Math Function and Divide Block Support" on page 56

- "Optional Suppression of Reset Logic Generation for Selected Delay Blocks" on page 56

- "Enhanced Embedded MATLAB Function Block Support" on page 57

- "Stateflow Chart Support Supports Complex Data Type" on page 60

- "hdlnewcontrolfile Function Generates Control Files Automatically" on page 61

- "Integrating FPGA Vendor Tools with Simulink® HDL Coder" on page 61

- "Timing Controller Optimization for Multirate Models" on page 61

- "Enhanced modelscope Syntax Increases Portability of Control Files" on page 62

• "Limited Variable-Step Solver Support" on page 63

### **Complex Data Type Support**

The coder now supports use of signals of complex data type.

You can use complex signals in the test bench without restriction.

In the device under test (DUT) selected for HDL code generation, support for complex signals is limited to a subset of the blocks supported by the coder. Some restrictions apply for some of these blocks. These blocks are listed in "Blocks That Support Complex Data".

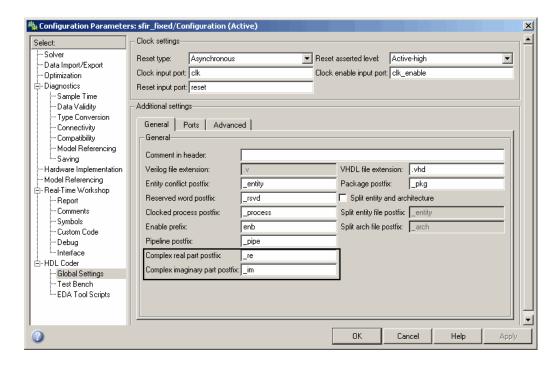

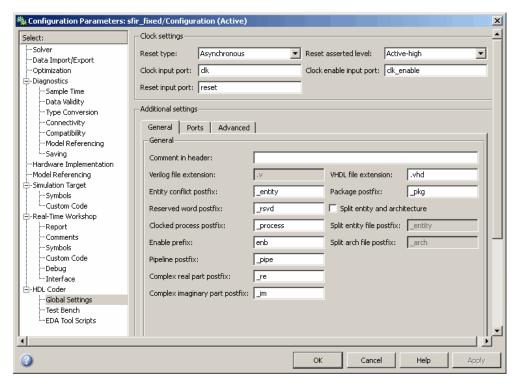

#### **New Options Supporting Complex Data Types**

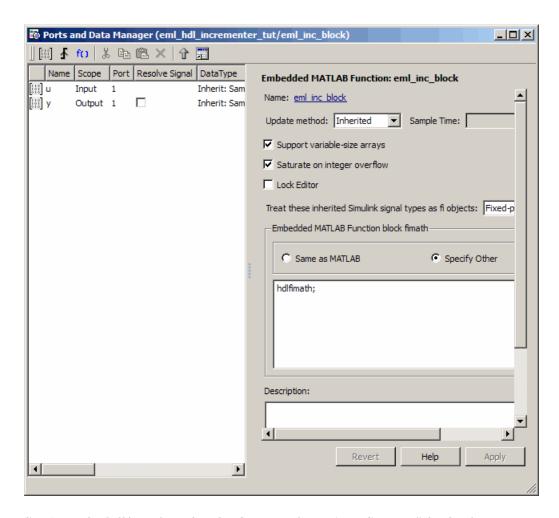

Two new code generation options have been added to help you customize naming conventions for the real and imaginary components of complex signals in generated HDL code. These options are available to the **Global Settings** / **General** pane in the **HDL Coder** pane of the Configuration Parameters dialog box, as shown in the following figure.

The Complex real part postfix option (and the corresponding ComplexRealPostfix CLI property) specifies a string to be appended to the names generated for the real part of complex signals. The default postfix is '\_re'. See also "Complex real part postfix".

The Complex imaginary part postfix option (and the corresponding ComplexImagPostfix CLI property) specifies a string to be appended to the names generated for the imaginary part of complex signals. The default postfix is 'im'. See also "Complex imaginary part postfix".

### **Test Bench Enhancements**

This release includes significant enhancements to test bench generation.

#### **Test Bench Supports Complex Data Type**

You can use complex signals in the test bench without restriction. Use of complex signals within the DUT is limited to a subset of supported blocks. See also "Complex Data Type Support" on page 49.

#### **New Test Bench Options and Properties**

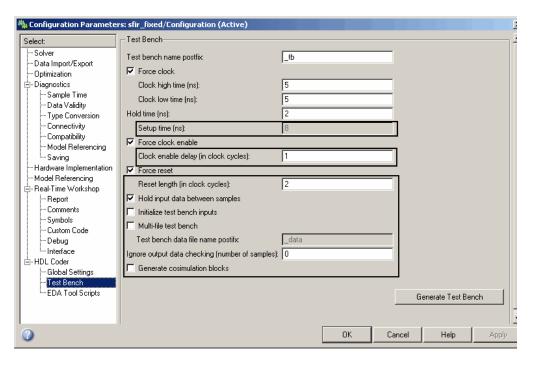

A number of options have been added to the **HDL Coder** / **Test Bench** pane of the Configuration Parameters dialog box, as shown in the following figure.

Most of the new options have a corresponding command-line property. The following table lists the new options and their corresponding CLI properties, and provides hyperlinks to the relevant documentation.

| GUI Option                                                                                   | Command-line Property                                                                               |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Setup time: See "Setup time (ns)"                                                            | This is a display-only field. It does not have a corresponding user-settable command-line property. |

| Clock enable delay (in clock cycles): See "Clock enable delay (in clock cycles)"             | TestBenchClockEnableDelay                                                                           |

| Reset length: See "Reset length (in clock cycles)"                                           | ResetLength                                                                                         |

| Hold input data between samples: See "Hold input data between samples"                       | HoldInputDataBetweenSamples                                                                         |

| Initialize test bench inputs: See "Initialize test bench inputs"                             | InitializeTestBenchInputs                                                                           |

| Multi-file test bench : See "Multi-file test bench"                                          | MultifileTestBench                                                                                  |

| Test bench data file name postfix: See "Test bench data file name postfix"                   | TestBenchDataPostFix                                                                                |

| Ignore test bench data checking:<br>See "Ignore output data checking<br>(number of samples)" | IgnoreDataChecking                                                                                  |

| Generate cosimulation blocks:<br>See "Cosimulation blocks"                                   | GenerateCoSimBlock                                                                                  |

## Additional Blocks Supported for HDL Code Generation

The coder now supports the following blocks for HDL code generation:

• Communications Blockset/Comm Sources/Sequence Generators/PN Sequence Generator

(This block requires Communications Blockset  $^{TM}$ .)

- Signal Processing Blockset/Multirate Filters/CIC Decimation

- Signal Processing Blockset/Multirate Filters/FIR Decimation

- Signal Processing Blockset/Signal Operations/NCO

- Signal Processing Blockset/Signal Processing Sources/Sine Wave

- Simulink/Discontinuities/Saturation

- Simulink/Discrete/Discrete-Time Integrator

- Simulink/Math Operations/Real-Imag to Complex

- Simulink/Math Operations/Complex to Real-Imag

- Simple Dual Port RAM (see also "Additional RAM Blocks" on page 55.)

- Single Port RAM (see also "Additional RAM Blocks" on page 55.)

See "Summary of Block Implementations" for a complete listing of blocks that are currently supported for HDL code generation.

### **Enhanced Pipelining Support**

In the previous release, the coder introduced output pipelining support for many block implementations (see "OutputPipeline"). In this release, pipelining support has been significantly expanded and enhanced. The following sections discuss new pipelining features.

#### **Input Pipelining**

You can now specify generation of input pipeline registers for selected blocks. To do this, invoke the new block implementation parameter {'InputPipeline', nStages} in a control file. The parameter value (nStages) specifies the number of input pipeline stages (pipeline depth) in the generated code. See "InputPipeline" for further information.

Most HDL block implementations support InputPipeline. See "Summary of Block Implementations" for a complete list of block implementations and their parameters.

## Automatic Pipeline Insertion for Embedded MATLAB Function Block and Stateflow Chart

In this release, the coder introduces *automatic pipeline insertion*, a special optimization for HDL code generated from Embedded MATLAB Function blocks or Stateflow charts. Automatic pipeline insertion is performed when the {'OutputPipeline', nStages} parameter is specified for these blocks. When you specify OutputPipeline, the coder inserts internal pipeline stages into the HDL code generated for these blocks (rather than at the output of the HDL code) whenever possible. The nStages argument defines the number of pipeline stages to be inserted.

Automatic pipeline insertion lets you achieve higher clock rates in your HDL applications, at the cost of some latency caused by the introduction of pipeline registers.

See "Distributed Pipeline Insertion for Embedded MATLAB Function Blocks" for a detailed description of this feature.

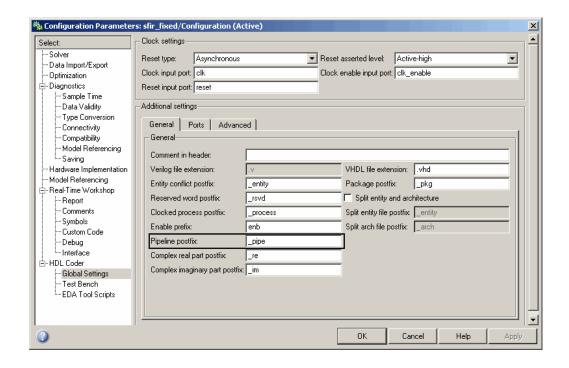

#### **Customizable Pipeline Register Names**

When generating code for pipeline registers, the coder appends a postfix string to names of input or output pipeline registers. The default postfix string is \_pipe. You can now customize the postfix string. To specify the postfix, use the **Pipeline postfix** option in the **Global Settings / General** pane in the **HDL Coder** pane of the Configuration Parameters dialog box (see the following figure). Alternatively, you can pass the desired postfix string in the makehdl property PipelinePostfix. See "Pipeline postfix" for an example.

#### **Additional RAM Blocks**

The coder now supports two new RAM blocks, supplementing the previously supported Dual Port RAM block:

- Simple Dual Port RAM: This block is identical to the Dual Port RAM, but does not have a data output at the write port. If data output at the write port is not required, you can achieve better RAM inferring with synthesis tools by using the Simple Dual Port RAM block rather than the Dual Port RAM block.

- Single Port RAM: This block provides data input, write address and write enable, and data output ports. The block GUI includes a **Output data** during write drop-down menu, providing options that control how the generated RAM handles data that is read into the RAM during a write operation.

See "RAM Blocks" for detailed information on RAM blocks.

### **Enhanced Math Function and Divide Block Support**

The coder now supports a wider range of functions and algorithms for the Math Function and Divide blocks, as follows:

- The Math Function block reciprocal operation is now supported. Implementations using either hardware divide (HDL / operator) or iterative Newton algorithm are available.

- The Math Function block conj function is now supported.

- The Math Function block sqrt function implementations now support a choice of multiply/add, bitset shift/addition, or iterative Newton algorithms.

- The Math Operations/Divide block reciprocal operation now supports implementations using either hardware divide (HDL / operator) or the iterative Newton algorithm.